Bootstrap bias circuit assignment

Bootstrapped bias

1.1 Design of series feedback amplifier

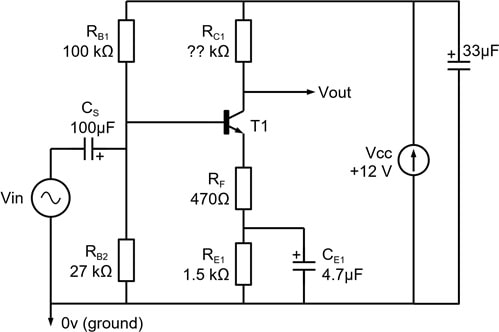

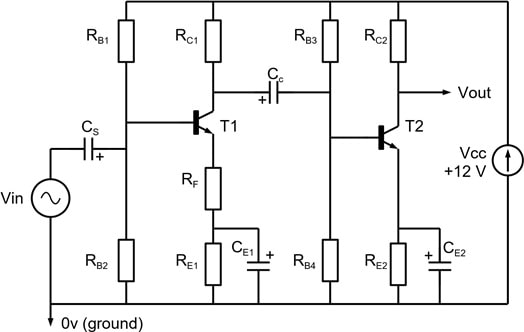

The partially designed and constructed series feedback circuit is shown in Figure 1. A Multisim implementation of the circuit (see Fig. 1a) is available for download from the ORB, but note that the value for the collector resistor is set at 0 Ω which is not correct!

Figure 1. Series feedback amplifier using BJT.

Design, calculation and simulation

To save time in the laboratory, it is best to do the following calculations in advance of the experimental work.

- Calculate a value for RC1 to achieve a mid-band voltage gain of approximately -10.

- Determine the bias conditions for the transistor (i.e. collector voltage, base voltage, emitter voltage, collector current and emitter current).

- Check with your calculated value of R C1 that the collector voltage can swing both above and below its bias level by approximately equal amounts. Why is this a desirable feature?

- Confirm that for the component values shown in Figure 1 the 3-dB break frequency at low frequency is determined mainly by CE1, RE1 and RF. Hence calculate the low-frequency breakpoint.

- Calculate the mid-band input resistance of the amplifier assuming that both C S and CE1 have negligible reactance. If transistor base-collector current gain β increases from 150 to 300 what percentage change in input resistance occurs?

- What is the ultimate rate of attenuation with frequency (dB/octave) at very low frequency?

- Figure 1 includes a 33µF capacitor (not shown in other circuits) connected across the power supply. It can be seen at the top right of the photograph in Appendix A, but does not affect the design aspects of the system. What is the essential function it performs, which is the same for any piece of electronic circuitry?

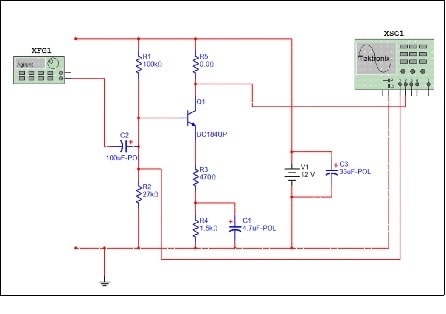

Figure 1a. Instrumented Multisim version of the amplifier – you can download the corresponding file from the ORB. Note that R5 (equivalent to Rc1 in Fig. 1) will have to be calculated and replaced.

- Construct the circuit on the breadboard, copying the layout in Appendix A if you have not done this before. The original used for the photograph will be available for inspection in the laboratory. The layout copies the actual circuit diagram quite closely. Be very careful with the transistor connections which can vary: the most common version for the BC184 type is 'bce', left to right looking onto the leads with the curved part of the transistor upwards. This is different from Appendix C.

- Measure and plot the input-output amplitude response over a frequency range of 10 Hz to 1 MHz using either an AC millivoltmeter or a digital oscilloscope, and obtain a gain reading in decibels. Identify the mid-band gain and the low-frequency breakpoint and compare them against the predicted values. Is the gain accurately defined by a resistor ratio? If not, what might account for a small difference from –10?

- Measure the input resistance of the amplifier at 1 kHz and compare it to the theoretical prediction - if you are not sure of the very easy way to do the measurement, ask a demonstrator. What is the dominant factor that determines the input resistance?

- * Investigate the overload performance by progressively increasing the input signal amplitude until the output waveform is severely distorted. Some very subtle effects can be seen here, which you should record and explain, and certainly discuss with the lab staff.

- * Measure the upper 3dB cutoff frequency of the amplifier. This can be done either by extending the measurement range of (b) to (say) 10 MHz, but there are two quick ways to do it. The first is to set the output signal amplitude at some convenient level, say 2 V pk-pk, for an input at 1 kHz, then increase the signal generator output frequency until the output voltage drops to the level equivalent to -3dB. The second method measures rise (or fall) time in response to a squarewave input signal. Then it can be shown that, in simple cases like this:

Bandwidth × Risetime ≈ 0.35

- * Use the oscilloscope to examine and record the amplifier output for very low frequency squarewave inputs (1 – 10 Hz). Explain what you see, but note that it is essential for the oscilloscope input coupling to be set to DC for this to work properly.

Appendix B gives more information on time-domain (risetime/falltime) measurements using the oscilloscope.

1.2 Bootstrap bias circuit

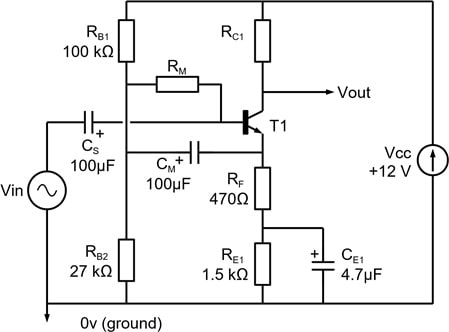

Figure 2. Bootstrap bias circuit.

In this experiment you are required to modify the amplifier circuit of Figure 1 to incorporate bootstrap biasing as shown in Figure 2. If you are not certain what 'bootstrapping' means, ask a demonstrator, but in summary it increases the apparent value of the resistor RM for AC signals so reducing the load it imposes on the input signal[1].

Assuming that the reactance of all capacitors is negligible, calculate the mid-band voltage gain between the input and an output taken at the transistor emitter. Then, taking bootstrapping into account, calculate RM so that its contribution to the mid-frequency input resistance is approximately 100 kΩ.

A suggested value for CM is 100 µF – not critical.

Measurements

- Add RM and CM to the circuit, noting the correct polarity for CM. Re-measure the bias conditions of the amplifier and confirm that the introduction of RM has not had a significant effect.

- Measure both mid-band input resistance and voltage gain and compare against your earlier measurements and calculation. Account theoretically for any change in input resistance.

- * Note that the frequency response at very low frequencies may show an undesirable resonance peak. Justify your measured results by analysing the low frequency transfer function and show that at low frequency the input impedance can appear partially inductive, which can resonate with the input coupling capacitor. Using Multisim, investigate the low frequency response of the amplifier for a range of CS from 0.1 µF to 100 µF. A very low frequency squarewave input may give useful insights here.

2 Multi-stage amplifier

2.1 AC coupled, cascaded npn transistor stages

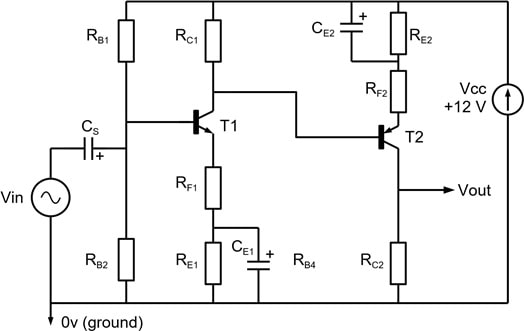

Construct the multi-stage amplifier shown in Figure 3 by adding a 'copy' of the circuit in Figure 1, but note that the second stage has no AC emitter degeneration (i.e. RF2 = 0 Ω) so you will need to choose an appropriate value for RE2. Cc should be connected to the collector of the first transistor. Measurements

A problem. When doing the following measurements, as noted previously, you should monitor the output signal on the oscilloscope to ensure that it is not distorted. Because the overall gain of the two stages is so large it will be impossible to reduce the signal generator output sufficiently to avoid output 'clipping'. The solution is to insert an attenuator at the input; a potential divider using 1000 ohm and 10 ohm resistors is recommended (or 990 (=890+100) and 10 ohms if you want a very precise factor of 100!). Measure the signal generator voltage to the amplifier at the input to the attenuator, then take its attenuation factor into account in the gain calculation – the signal at the amplifier input itself will be too small to measure easily with the standard lab instruments.

With the two amplifiers connected together:

- Measure the mid-band gain from input to the output of the first stage and compare this with the gain measured in Section 1.1.

- Why is the overall gain not equal to the product of the individual stage gains when they are measured with the two stages disconnected from each other?

- Measure the mid-band gain from input to the output of the second stage. Compare your results with the theoretical gain incorporating relevant information from the bias conditions.

- Measure the overall frequency response over the range 10 Hz to 1 MHz and relate this to the gains determined above.

- * Find the upper 3dB cutoff frequency of the 2-stage amplifier.

- * A configuration like this would not be used in any practical application, and both stages would typically have feedback. Modify the second stage to do this: the easiest way is simply to copy the emitter circuitry of stage 1. Make the individual stage gains both nominally 10, and measure overall performance.

Figure 3. Two-stage amplifier circuit.

2.2 Direct coupled npn-pnp stages

This circuit (Figure 4) uses complementary npn and pnp transistors.

(a) Design and build the second stage of the two-stage amplifier as shown in Figure 4, a useful configuration that reduces the number of biasing components and also omits the coupling capacitor. The design reuses the idea from 2.1(f) of both stages having series feedback (i.e. insert RF2/CE2 in the emitter connection of T2).

Calculate RE2 + RF2 to bias T2 at the same collector current as the common-emitter amplifier in Section 1.1 and make the nominal gain of the second stage also 10.

You should find that the overall gain of this version of the 2-stage design is more closely related to the gains of the individual stages. Explain why.

Figure 4 Direct-coupled two-stage amplifier using npn and pnp devices. A suitable pnp transistor for T2 is BC214 (complement to BC184). Remember to include a decoupling capacitor across the power supply lines.

[1] Very simply, the voltage 'gain' from base to emitter in this circuit is slightly less than 1. This means that the AC signals at each end of RM are nearly the same, so the current change due to an input change Dv is significantly smaller than it would have been.